# DELTA-SIGMA MODULATORS WITH LOW OVERSAMPLING RATIOS

by

Trevor C. Caldwell

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Trevor C. Caldwell 2010

## DELTA-SIGMA MODULATORS WITH LOW OVERSAMPLING RATIOS

Trevor C. Caldwell

Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering University of Toronto, 2010

### ABSTRACT

This dissertation explores methods of reducing the *oversampling ratio* (OSR) of both *delta-sigma* ( $\Delta\Sigma$ ) modulators and incremental data converters. The first reduced-OSR architecture is the high-order cascaded  $\Delta\Sigma$  modulator. These  $\Delta\Sigma$  modulators are shown to reduce the in-band noise sufficiently at OSRs as low as 3 while providing power savings. The second low OSR architecture is the high-order cascaded incremental data converter which possesses *signal-to-quantization noise ratio* (SQNR) advantages over equivalent  $\Delta\Sigma$  modulators at low OSRs. The final architecture is the time-interleaved incremental data converter where two designs are identified as potential methods of increasing the throughput of low OSR incremental data converters. A prototype chip is designed in 0.18 µm CMOS technology which can operate in three modes by simply changing the resetting clock phases. It can operate as an 8-stage pipeline *analog-to-digital* (A/D) converter, an 8<sup>th</sup>-order cascaded  $\Delta\Sigma$  modulator, and an 8<sup>th</sup>-order cascaded incremental data converter with an OSR of 3.

## Acknowledgements

This dissertation has only come to completion with the help and support of numerous individuals. First I must thank my supervisor Prof. David Johns for his invaluable advice and guidance throughout the course of this degree. I thank Prof. Ken Martin, Ahmed Gharbiya and Richard Schreier who provided countless suggestions throughout my research. I also thank my supervisory committee of Prof. Tony Chan Carusone, Prof. Wai Tung Ng, Prof. Glenn Gulak and Prof. Gabor Temes for their feedback.

I gratefully acknowledge funding from the Natural Sciences and Engineering Research Council of Canada, the Ontario Graduate Scholarship in Science and Technology, and the Robert Bosch Corporation, as well as fabrication services and CAD tools from CMC Microsystems.

I spent a lot of time at the university over the past several years, and it was the people around me that made it enjoyable. For that, I am indebted to my friends in the electronics group, and my teammates and coaches at UTTC.

Finally, I would not have accomplished anything without the support of my family. I thank my brother Daryl, my sister Lauren, and especially my parents Douglas and Cheryl for everything they have done to get me this far in my education. Most importantly I thank my girlfriend Paula who has been at my side for the entire degree, through the dizzying highs, the terrifying lows, and everything in between.

# Contents

| Chapter | 1 Ir              | ntroduction                               | 1  |

|---------|-------------------|-------------------------------------------|----|

| 1.1     | Motiva            | tion                                      | 1  |

| 1.2     | Current           | t Literature                              | 2  |

|         | 1.2.1             | High-Speed $\Delta\Sigma$ Modulators      | 2  |

|         | 1.2.2             | High-Speed Pipeline A/D Converters        | 3  |

| 1.3     | Outline           |                                           | 4  |

| Chapter | 2 B               | ackground Information                     | 6  |

| 2.1     | $\Delta\Sigma$ Mo | dulators                                  | 6  |

|         | 2.1.1             | Single-Stage $\Delta\Sigma$ Modulators    | 7  |

|         | 2.1.2             | Cascaded $\Delta\Sigma$ Modulators        | 8  |

| 2.2     | Increm            | ental Data Converters                     | 11 |

|         | 2.2.1             | Dual-Slope A/D Converters                 | 11 |

|         | 2.2.2             | First-Order Incremental A/D Converters    | 13 |

|         | 2.2.3             | Higher-Order Incremental A/D Converters   | 16 |

|         | 2.2.4             | Input-Referred Noise                      | 21 |

| 2.3     | Pipelin           | e Data Converters                         | 22 |

|         | 2.3.1             | Architecture                              | 22 |

|         | 2.3.2             | Offsets                                   | 24 |

|         | 2.3.3             | Cascaded like a MASH                      | 25 |

| 2.4     | Time-In           | nterleaving                               | 26 |

|         | 2.4.1             | Nyquist-Rate A/D Converters               | 26 |

|         | 2.4.2             | $\Delta\Sigma$ Modulators                 | 26 |

| 2.5     | A/D Tr            | ade-Offs: Power, Resolution and Bandwidth | 28 |

|         | 2.5.1             | Power and Bandwidth                       | 28 |

|         | 2.5.2             | Bandwidth and Resolution                  | 29 |

|         | 2.5.3             | Resolution and Power                      | 30 |

|         | 2.5.4             | Figure of Merit                           | 30 |

| Chapter | · 3 🛛 🛆 | $\Sigma$ Modulators at Low OSRs              | 31 |

|---------|---------|----------------------------------------------|----|

| 3.1     | Operat  | ion at Low OSRs                              | 31 |

|         | 3.1.1   | Increased Noise                              | 31 |

|         | 3.1.2   | Comparison with a Nyquist-Rate A/D Converter | 32 |

| 3.2     | Single  | -Stage vs. Cascaded $\Delta\Sigma$           | 33 |

|         | 3.2.1   | Single-Stage Architecture                    | 34 |

|         | 3.2.2   | Cascaded Architecture                        | 35 |

| 3.3     | Propos  | ed High-Order Cascaded $\Delta\Sigma$        | 35 |

|         | 3.3.1   | Architecture                                 | 35 |

|         | 3.3.2   | Power Efficiency                             | 37 |

|         | 3.3.3   | Anti-Aliasing and Decimation                 | 42 |

| Chapter | :4 I    | ncremental Data Converters at Low OSRs       | 44 |

| 4.1     | Operat  | ion at Low OSRs                              | 44 |

|         | 4.1.1   | Incremental vs. $\Delta\Sigma$               | 44 |

|         | 4.1.2   | Pipeline Equivalency                         | 47 |

|         | 4.1.3   | Removing the Input S/H                       | 48 |

|         | 4.1.4   | Resetting Efficiency                         | 52 |

| 4.2     | Time-I  | Interleaved Incremental A/D Converters       | 55 |

|         | 4.2.1   | Time-Interleaving                            | 55 |

|         | 4.2.2   | Signal Transfer Function                     | 57 |

|         | 4.2.3   | Matching and Calibration                     | 61 |

| 4.3     | Propos  | ed High-Order Incremental A/D Converter      | 63 |

|         | 4.3.1   | Architecture                                 | 63 |

|         | 4.3.2   | Power and Design Comparisons                 | 64 |

|         | 4.3.3   | Anti-Aliasing and Decimation                 | 68 |

| Chapter | ·5 C    | Circuit Design                               | 69 |

| 5.1     | A/D Sy  | ystem                                        | 69 |

|         | 5.1.1   | Architecture                                 | 69 |

|         | 5.1.2   | Target Specifications                        | 71 |

|         | 5.1.3   | Individual Stage                             | 71 |

|         | 5.1.4   | Noise Allocation                             | 71 |

| 5.2     | Operat  | ional Transconductance Amplifier             | 73 |

|         | 5.2.1   | DC Gain                                      | 73 |

|         | 5.2.2   | Bandwidth                                    | 74 |

|         | 5.2.3   | Slewing                                      | 76 |

|         | 5.2.4   | Topology                                     | 76 |

|         | 5.2.5   | Thermal Noise                                | 78 |

|         | 5.2.6   | Choice of Effective Voltage                  | 80 |

|         | 5.2.7   | Design                                       | 81 |

|         | 5.2.8   | Gain-Boosting                                | 84 |

| 5.3     | 5.3.1<br>5.3.2 | Main OTA Common-Mode Feedback.Gain-Boosted OTA.Stage Scaling.Circuits.Summing Analog-to-Digital Converter.Digital-to-Analog Converter. | 94<br>95<br>97<br>97<br>100 |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|         | 5.3.3<br>5.3.4 | Switches                                                                                                                               |                             |

|         | 5.3.5          | Analog Multiplexer                                                                                                                     |                             |

|         |                | Layout                                                                                                                                 |                             |

| 5.4     |                | Simulations                                                                                                                            |                             |

| Chapter | 6 Ex           | xperimental Results                                                                                                                    | 112                         |

| 6.1     |                | ••••••••••••••••••••••••••••••••••••••                                                                                                 |                             |

|         | 6.1.1          | Fabricated Chip                                                                                                                        |                             |

|         | 6.1.2          | Printed Circuit Board                                                                                                                  |                             |

|         | 6.1.3          | Equipment                                                                                                                              | 114                         |

| 6.2     | Pipeline       | e Mode                                                                                                                                 | 115                         |

|         | 6.2.1          | Bias Voltages                                                                                                                          | 116                         |

|         | 6.2.2          | Static Testing                                                                                                                         | 116                         |

|         | 6.2.3          | Dynamic Testing                                                                                                                        | 120                         |

| 6.3     | ΔΣ Μοσ         | de                                                                                                                                     | 122                         |

| 6.4     | Increme        | ental Mode                                                                                                                             | 126                         |

| 6.5     | Discuss        | ion                                                                                                                                    | 128                         |

| Chapter | 7 C            | onclusions                                                                                                                             | 130                         |

| 7.1     | Summa          | ry                                                                                                                                     | 130                         |

| 7.2     |                | utions                                                                                                                                 |                             |

| 7.3     |                | Directions                                                                                                                             |                             |

|         | 7.3.1          | Higher-Order Individual Stages                                                                                                         |                             |

|         | 7.3.2          | Time-Interleaved Incremental Data Converters                                                                                           |                             |

|         | 7.3.3          | Decimation Filter                                                                                                                      |                             |

|         | 7.3.4          | OTA Power Down                                                                                                                         |                             |

|         | 7.3.5          | Continuous-Time Cascaded Incremental Converters                                                                                        | 133                         |

| Appendi | ices           |                                                                                                                                        | 134                         |

| Appendi | ix A R         | esolution of an Incremental A/D Converter                                                                                              | 135                         |

| A.1     | First-O        | rder                                                                                                                                   | 135                         |

| A.2     | Second         | -Order Single-Stage                                                                                                                    | 136                         |

| A.3     | Second         | -Order Cascaded                                                                                                                        | 138                         |

| A.4     | Extensi        | on to Higher-Order                                                                                                                     | 141                         |

| Append      | ix B Finite DC Gain in Incremental A/D Converters | 143   |

|-------------|---------------------------------------------------|-------|

| <b>B</b> .1 | DC Gain Requirements                              | . 143 |

| Append      | ix C Unwinding the Incremental                    | 147   |

| C.1         | Time-Interleaved Algorithmic Data Converters      | . 147 |

| C.2         | Time-Interleaved Incremental Data Converters      | . 149 |

| Referen     | ces                                               | 152   |

# List of Tables

| 1.1        | Recently published experimental results for high-speed continuous-time (C) and discrete-time (D) $\Delta\Sigma$ modulators at low OSRs in CMOS technology, in order of increasing signal bandwidth.                                                     | 3   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2        | Recently published experimental results for high-speed pipeline A/D converters in CMOS technology.                                                                                                                                                      | 4   |

| 2.1        | Relative input-referred noise power for incremental A/D converters for various OSRs and orders. The results are normalized to the expected input-referred noise power for an oversampled A/D converter where the noise is $1/M$ for an OSR of $M$       | 22  |

| 3.1        | OSR where noise power in $\Delta\Sigma$ is equal to noise power in Nyquist-rate A/D                                                                                                                                                                     | 33  |

| 5.1        | OSK where holse power in $\Delta Z$ is equal to holse power in hyperstrate $A/D$                                                                                                                                                                        | 55  |

| 4.1<br>4.2 | SQNR Comparison of $\Delta\Sigma$ and incremental A/D converters at low OSRs<br>Input-referred noise power for each stage of an 8 <sup>th</sup> -order incremental A/D converter with an OSR of 3, and 8 stages of a pipeline A/D converter with an OSR | 45  |

|            | of 3                                                                                                                                                                                                                                                    | 67  |

| 4.3        | Comparison of anti-aliasing and decimation filters for an 8 <sup>th</sup> -order incremental                                                                                                                                                            |     |

|            | A/D converter, an 8-stage pipeline converter, and an 8 <sup>th</sup> -order $\Delta\Sigma$ modulator                                                                                                                                                    | 68  |

| 5.1        | Sizing for gain-booster $A_P$ (Fig. 5.15)                                                                                                                                                                                                               | 88  |

| 5.2        | Sizing for gain-booster $A_N$ (Fig. 5.6)                                                                                                                                                                                                                | 88  |

| 5.3        | Sizing for CMFB circuit of Fig. 5.16.                                                                                                                                                                                                                   | 90  |

| 5.4        | Sizing for CMFB circuit of Fig. 5.17.                                                                                                                                                                                                                   | 90  |

| 5.5<br>5.6 | Relative stage scaling for the main OTA and gain-boosters                                                                                                                                                                                               | 97  |

| 5.7        | without thermal noise                                                                                                                                                                                                                                   |     |

| 6.1        | Simulated and measured bias voltages for the OTAs and gain-boosters from the first, second and fourth stages. Simulated results are taken from the TT corner at $80 ^{\circ}$ C.                                                                        | 117 |

| 6.2 | Stage 1 simulated and measured bias voltages on both the TT and SS corners at                    |    |

|-----|--------------------------------------------------------------------------------------------------|----|

|     | 80 °C. The measured results indicate that the test chip was fabricated between                   |    |

|     | the typical and slow corners                                                                     | 18 |

| 6.3 | Summary of experimental results for the 8-stage pipeline A/D converter (sim-                     |    |

|     | ulated results do not include thermal noise)                                                     | 23 |

| 6.4 | Summary of experimental results for the 8 <sup>th</sup> -order cascaded $\Delta\Sigma$ modulator |    |

|     | (simulated results do not include thermal noise)                                                 | 25 |

| 6.5 | Summary of experimental results for the 8 <sup>th</sup> -order cascaded incremental A/D          |    |

|     | converter (simulated results do not include thermal noise)                                       | 27 |

|     |                                                                                                  |    |

# List of Figures

| 2.1  | Spectral operation of a $\Delta\Sigma$ modulator.                                                                                                                                                                                                                 | 7  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | General architecture of a $\Delta\Sigma$ modulator characterized by the two loop filters                                                                                                                                                                          |    |

|      | $L_0(z)$ and $L_1(z)$ (without the decimation filter).                                                                                                                                                                                                            | 7  |

| 2.3  | Input feed-forward architecture for a general $\Delta\Sigma$ modulator (without the deci-                                                                                                                                                                         |    |

|      | mation filter).                                                                                                                                                                                                                                                   | 8  |

| 2.4  | General 2-stage cascaded $\Delta\Sigma$ modulator where loop filters $L_0(z)$ and $L_1(z)$ characterize the first stage, and $L_2(z)$ and $L_3(z)$ characterize the second stage                                                                                  | 9  |

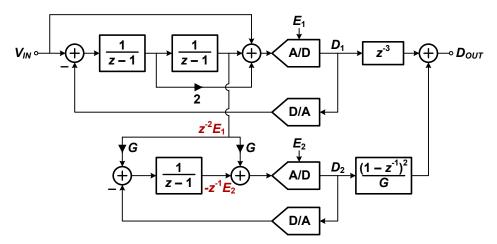

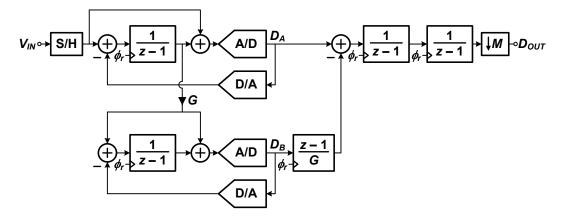

| 2.5  | Input feed-forward 2-1 cascaded $\Delta\Sigma$ modulator. The interstage gain G im-                                                                                                                                                                               |    |

|      | proves the resolution by $G$                                                                                                                                                                                                                                      | 11 |

| 2.6  | Dual-slope A/D converter. The input signal is integrated on $S_1$ while the reference voltage is integrated and subtracted from the input on $S_2$ . $\phi_1$ is operating at the sampling frequency $f_s$ . $T_1$ and $T_2$ are proportional to their respective |    |

|      | digital outputs.                                                                                                                                                                                                                                                  | 12 |

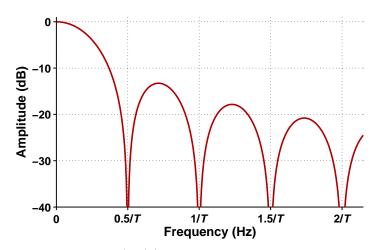

| 2.7  | Function $AT \sin(\omega T) / \omega T$ (the peak amplitude $AT$ is normalized to 0 dB). The                                                                                                                                                                      |    |

|      | spectral nulls are evident at integer multiples of $\pi$ for the argument $\omega T$ . For                                                                                                                                                                        |    |

|      | the dual-slope A/D converter, $T = 2^N T_s$                                                                                                                                                                                                                       | 14 |

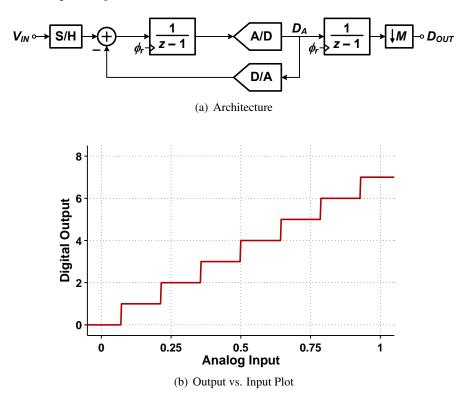

| 2.8  | Operation of a 1 <sup>st</sup> -order incremental A/D converter with an OSR of 7 and a                                                                                                                                                                            |    |

|      | binary quantizer, resulting in 8 output levels.                                                                                                                                                                                                                   | 15 |

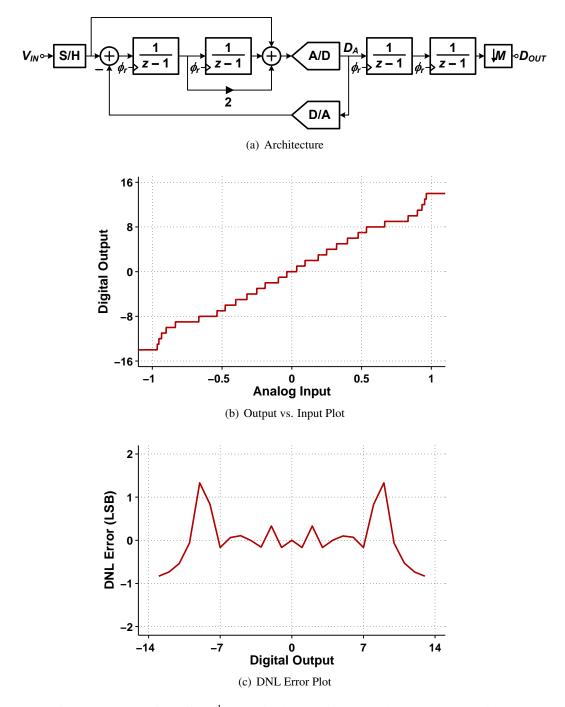

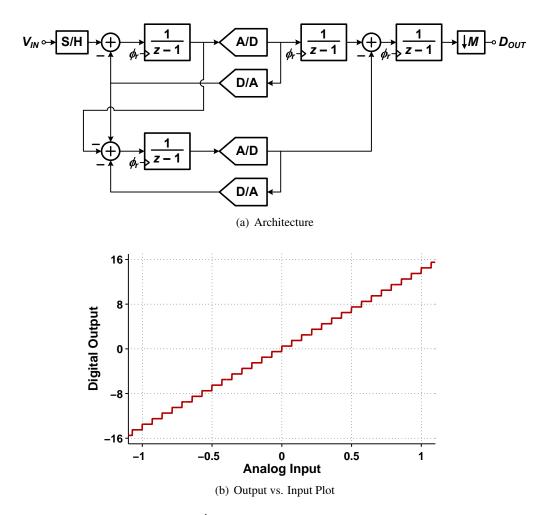

| 2.9  | Operation of a 2 <sup>nd</sup> -order single-stage incremental A/D converter with an OSR                                                                                                                                                                          |    |

|      | of 7 and a binary quantizer, resulting in 29 output levels                                                                                                                                                                                                        | 18 |

| 2.10 | Operation of a 2 <sup>nd</sup> -order cascaded incremental A/D converter with an OSR of                                                                                                                                                                           |    |

|      | 7 and 30 output levels                                                                                                                                                                                                                                            | 20 |

|      | Individual stage of a pipeline A/D converter.                                                                                                                                                                                                                     | 23 |

|      | Architecture of a pipeline A/D converter                                                                                                                                                                                                                          | 23 |

| 2.13 | Pipeline stage error signal in the presence of comparator offset with 4 com-                                                                                                                                                                                      |    |

|      | parator levels resolved.                                                                                                                                                                                                                                          | 24 |

| 2.14 | Pipeline stage in the presence of comparator offsets with 3 comparator levels                                                                                                                                                                                     |    |

|      | resolved                                                                                                                                                                                                                                                          | 25 |

| 2.15 | Two-stage pipeline redrawn to demonstrate its similarities with a cascaded $\Delta\Sigma$                                                                                                                                                                         |    |

|      | modulator. The integrators of the cascaded $\Delta\Sigma$ of Fig. 2.5 have been removed                                                                                                                                                                           |    |

|      | to generate this figure                                                                                                                                                                                                                                           | 26 |

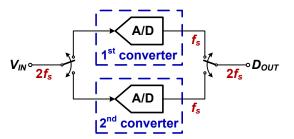

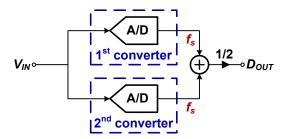

|      | Time-interleaved Nyquist-rate A/D converter.                                                                                                                            | 27  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

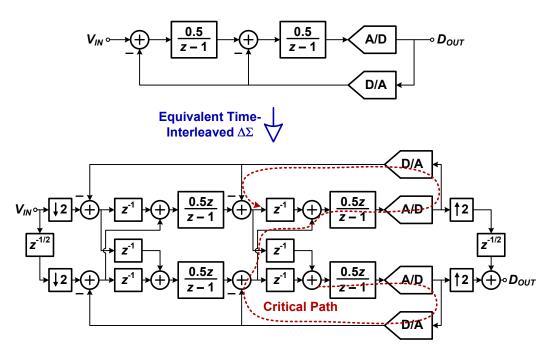

|      | Time-interleaved $\Delta\Sigma$ modulator.                                                                                                                              | 27  |

| 2.18 | Time-interleaved example of the power and bandwidth trade-off. Two time-interleaved converters double the power, but also double the throughput                         | 29  |

| 2.19 | Oversampling example of the bandwidth and resolution trade-off. The second half of the spectrum is perfectly filtered, resulting in half the signal bandwidth,          |     |

| 2.20 | and 3 dB less noise (since half the noise bins are ignored)                                                                                                             | 29  |

|      | parallel converters double the power, but reduce the noise by 3 dB                                                                                                      | 30  |

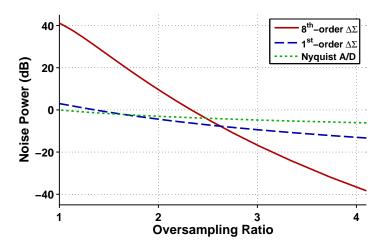

| 3.1  | Total In-Band Noise Power vs. OSR. The numbers are normalized to a Nyquist-<br>rate A/D converter with an OSR of 1. It is assumed that both A/D converters              |     |

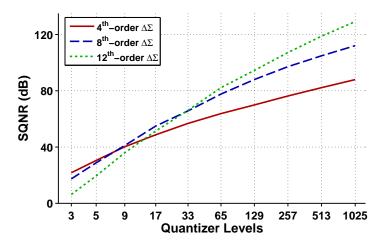

| 3.2  | have the same number of quantizer levels (i.e., same quantization noise power).<br>SQNR vs. Quantizer Levels. The maximum achievable SQNR for a 4 <sup>th</sup> -order, | 32  |

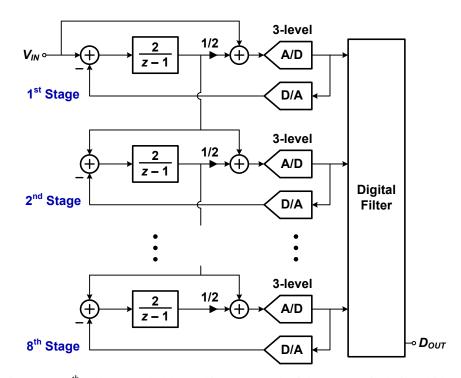

| 3.3  | $8^{\text{th}}$ -order and $12^{\text{th}}$ -order $\Delta\Sigma$ modulator at an OSR of 3                                                                              | 34  |

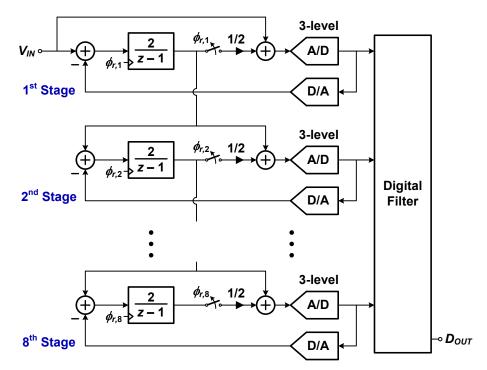

|      | with a 3-level quantizer and a weighted summer at the quantizer input                                                                                                   | 36  |

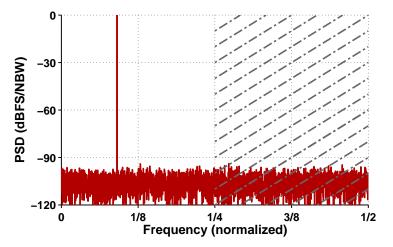

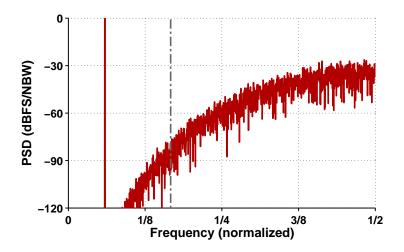

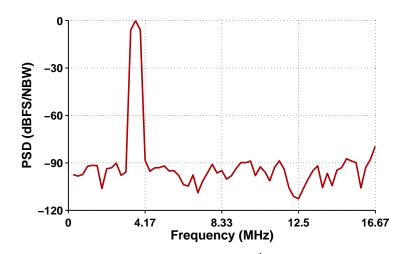

| 3.4  | Output spectrum for an 8 <sup>th</sup> -order cascaded $\Delta\Sigma$ (NBW = $3.7 \times 10^{-4}$ )                                                                     | 37  |

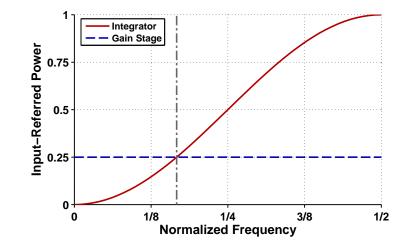

| 3.5  | Input-referred noise comparison through a gain stage and an integrator stage.<br>At an OSR of 3, the gain is equivalent at the signal band edge, but increasingly       |     |

| 3.6  | less for the integrator stage at higher OSRs                                                                                                                            | 38  |

|      | modulators.                                                                                                                                                             | 41  |

| 3.7  | Precision delaying gain stage.                                                                                                                                          | 41  |

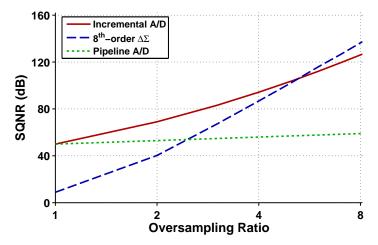

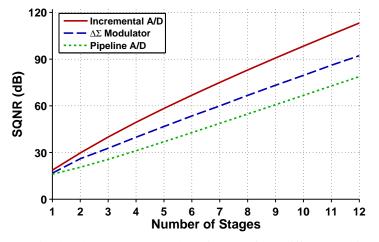

| 4.1  | Simulated SQNR vs. OSR for 3 different architectures. All three A/D converters have the same internal 3-level quantizers. Simulations for the incremental               | 4.6 |

| 4.2  | A/D converter match Eq. 4.2                                                                                                                                             | 46  |

|      | Eq. 4.2.                                                                                                                                                                | 47  |

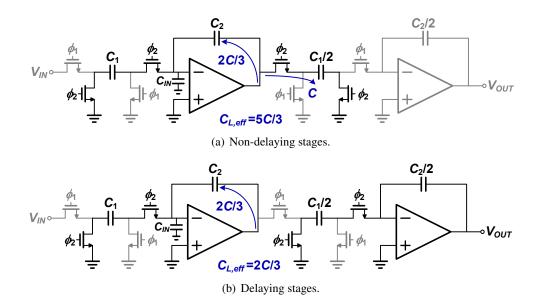

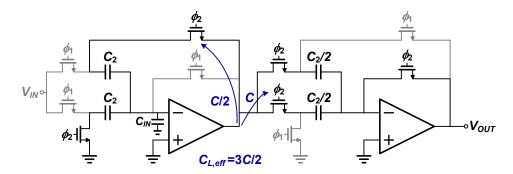

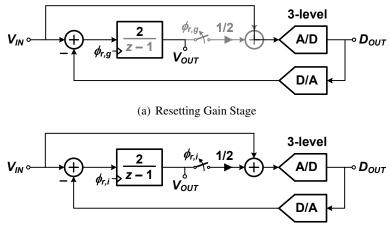

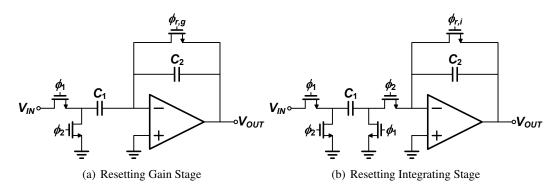

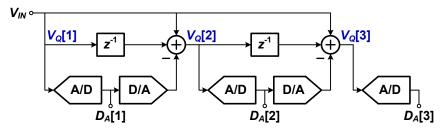

| 4.3  | The architectural difference between the stages of a pipeline A/D converter and an input feed-forward cascaded incremental A/D converter.                               | 48  |

| 4.4  | The circuit-level difference between a pipeline A/D converter and an incre-                                                                                             | 10  |

|      | mental A/D converter lies in the resetting sequence of the gain or integrating stage.                                                                                   | 49  |

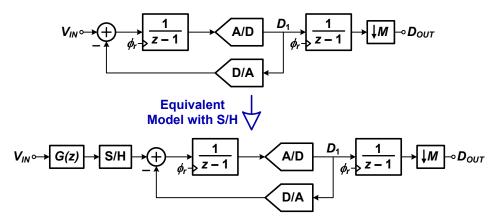

| 4.5  | Model of an incremental A/D converter with no S/H, and its equivalent model with an input S/H. $G(z)$ is not explicitly used, but it is the effective modification      | 77  |

|      | of the STF when the S/H is removed                                                                                                                                      | 50  |

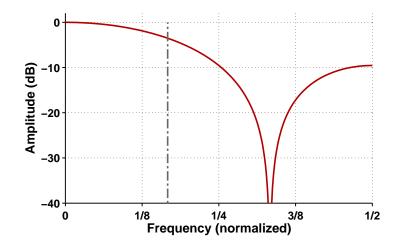

| 4.6        | G(z) for a 1 <sup>st</sup> -order incremental A/D converter with an OSR of 3                                                                                                | 51 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

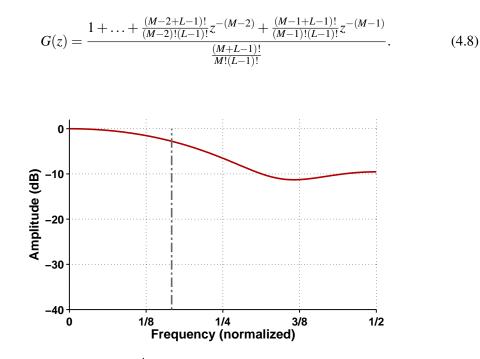

| 4.7        | G(z) for a 2 <sup>nd</sup> -order incremental A/D converter with an OSR of 3                                                                                                | 52 |

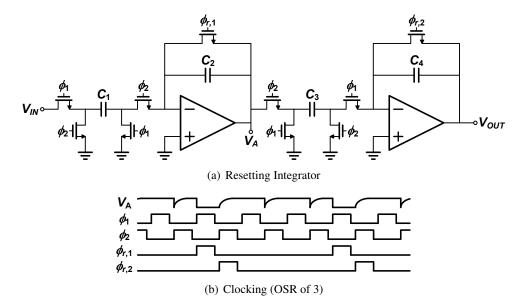

| 4.8        | Resetting scheme for two cascaded integrators in an incremental A/D converter.                                                                                              | 53 |

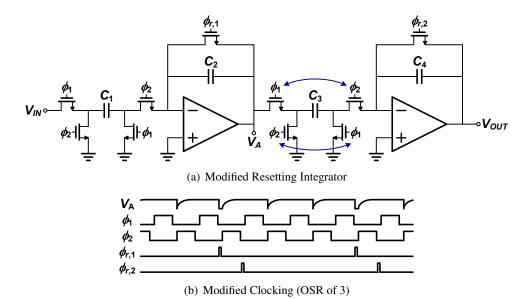

| 4.9        | Modified fully-delaying resetting scheme for two cascaded integrators in an                                                                                                 |    |

|            | incremental A/D converter.                                                                                                                                                  | 55 |

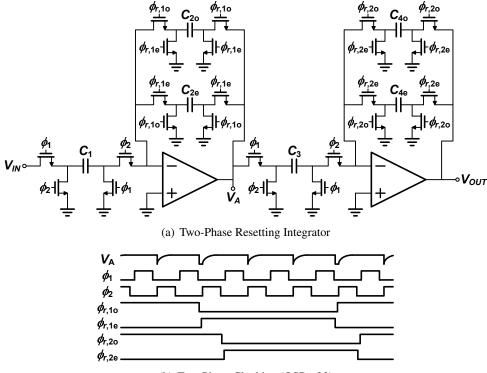

| 4.10       | Fully-delaying two-phase resetting scheme for two cascaded integrators in an                                                                                                |    |

|            | incremental A/D converter.                                                                                                                                                  | 56 |

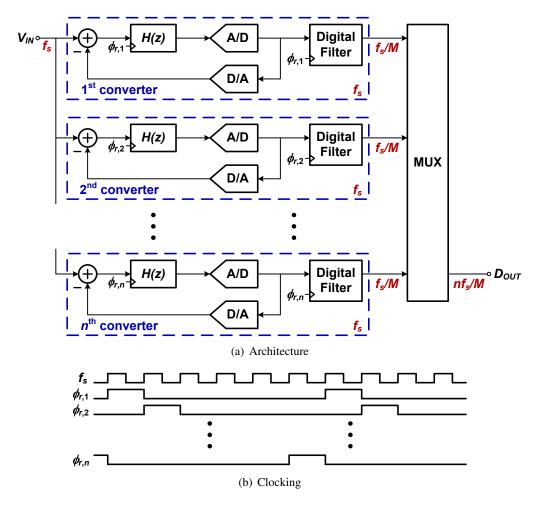

| 4.11       | Time-interleaved incremental A/D converter. The clocking scheme is such that                                                                                                |    |

|            | each individual converter resets in sequence.                                                                                                                               | 57 |

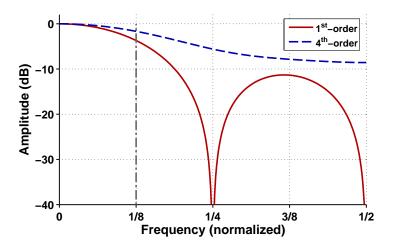

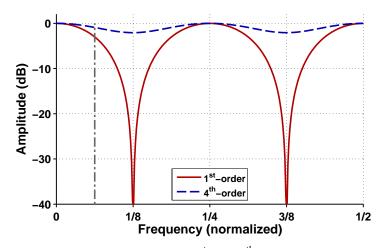

| 4.12       | STF for a 1 <sup>st</sup> - and 4 <sup>th</sup> -order incremental A/D converter with an OSR of 4                                                                           | 58 |

| 4.13       | STF for a 1 <sup>st</sup> - and 4 <sup>th</sup> -order incremental A/D converter with an OSR of 8                                                                           | 58 |

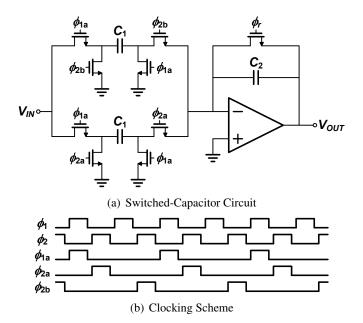

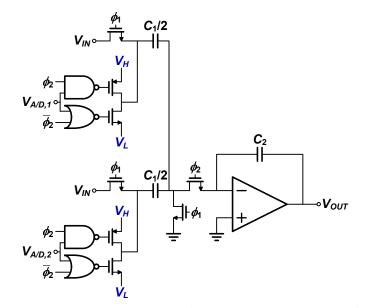

| 4.14       | Proposed double-sampled switching scheme. The clock $\phi_{1a}$ samples the input                                                                                           |    |

|            | twice on every second $\phi_1$ , while clock $\phi_2$ is divided into $\phi_{2a}$ and $\phi_{2b}$                                                                           | 60 |

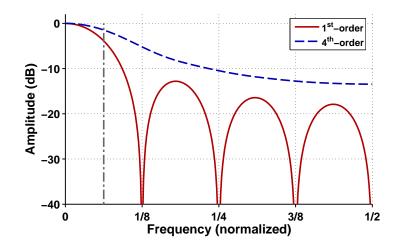

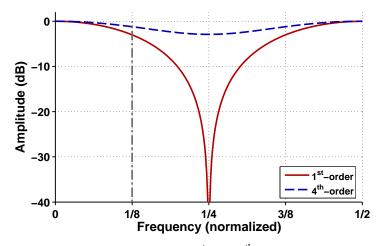

| 4.15       | Double-sampled STF for a 1 <sup>st</sup> - and 4 <sup>th</sup> -order incremental A/D converter with                                                                        |    |

|            | an OSR of 4                                                                                                                                                                 | 60 |

| 4.16       | Double-sampled STF for a 1 <sup>st</sup> - and 4 <sup>th</sup> -order incremental A/D converter with                                                                        |    |

|            | an OSR of 8                                                                                                                                                                 | 61 |

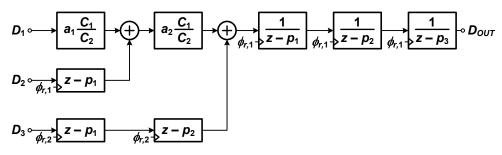

| 4.17       | Digital calibrating filter for a cascaded incremental A/D converter. A 3 <sup>rd</sup> -order                                                                               |    |

|            | structure is shown for simplicity, but it can be easily extended to an $L^{\text{th}}$ -order                                                                               |    |

|            | modulator where <i>L</i> digital paths combine to a final $D_{OUT}$                                                                                                         | 62 |

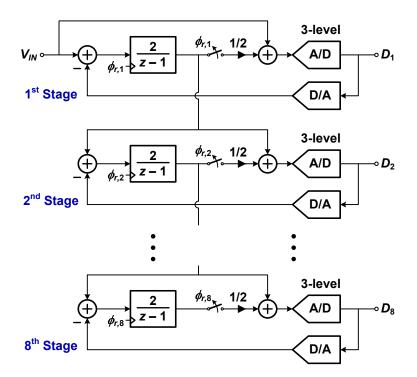

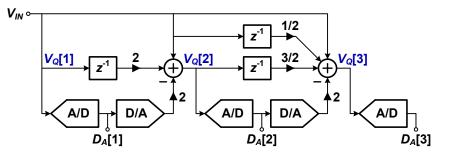

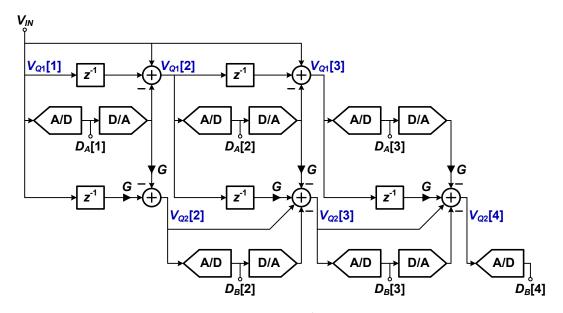

| 4.18       | Proposed incremental A/D architecture. Each stage is designed identically as a                                                                                              |    |

|            | 1 <sup>st</sup> -order input feed-forward stage with a 3-level quantizer                                                                                                    | 64 |

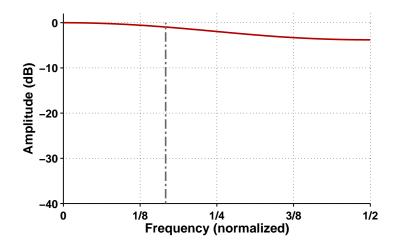

|            | STF for an 8 <sup>th</sup> -order incremental A/D converter with an OSR of 3                                                                                                | 64 |

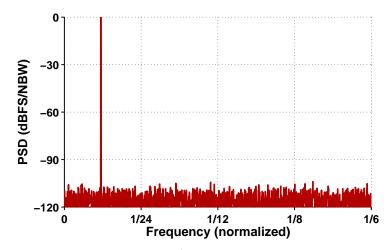

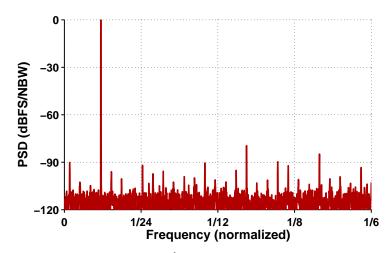

| 4.20       | Output spectrum for an 8 <sup>th</sup> -order incremental A/D converter (NBW = $1.2 \times$                                                                                 |    |

|            | $10^{-4}$ ).                                                                                                                                                                | 65 |

| 51         | A/D convertor prohitecture. Each stage is designed identically as a 1 <sup>st</sup> order                                                                                   |    |

| 5.1        | A/D converter architecture. Each stage is designed identically as a 1 <sup>st</sup> -order input feed-forward stage with a 3-level quantizer. The reset clock of each stage |    |

|            |                                                                                                                                                                             | 70 |

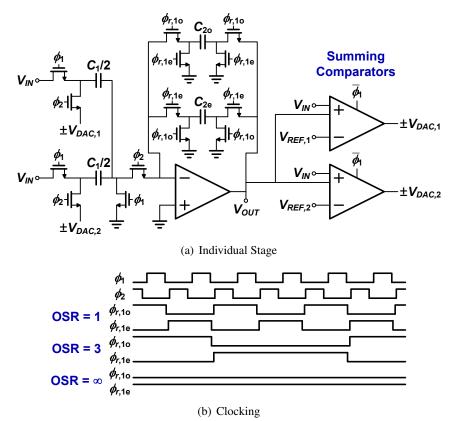

| 5.2        | is adjusted according to the desired A/D converter architecture                                                                                                             | 70 |

| 3.2        | two main blocks are the gain/integrator stage and the latched summing com-                                                                                                  |    |

|            | parator.                                                                                                                                                                    | 72 |

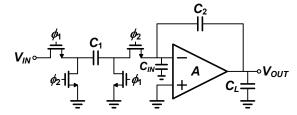

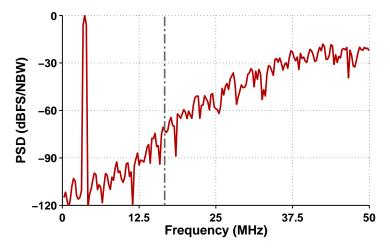

| 5.3        | Integrator with finite DC gain A, load capacitance $C_L$ , and input capacitance $C_{IN}$ .                                                                                 | 73 |

| 5.4        | Output spectrum for an $8^{\text{th}}$ -order incremental A/D converter with a first stage                                                                                  | 15 |

| 5.4        | DC gain of 5000 V/V (NBW = $1.2 \times 10^{-4}$ ).                                                                                                                          | 74 |

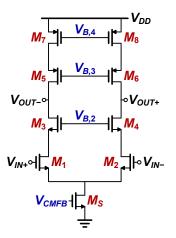

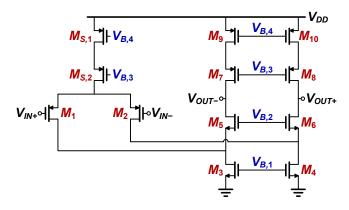

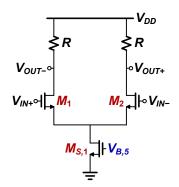

| 5.5        | Telescopic OTA                                                                                                                                                              | 77 |

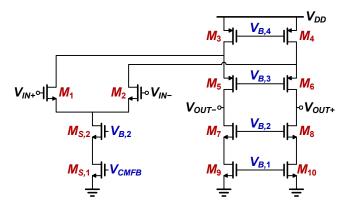

| 5.6        | Folded-cascode OTA.                                                                                                                                                         | 78 |

| 5.0<br>5.7 | Noise sources in a folded-cascode OTA. The cascoded transistors do not con-                                                                                                 | 70 |

| 5.1        | tribute significantly to the total noise.                                                                                                                                   | 79 |

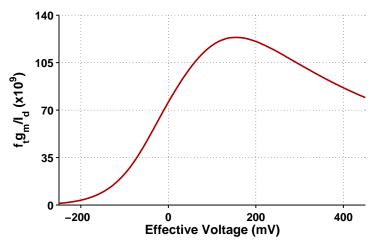

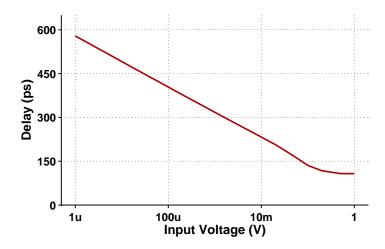

| 5.8        | Speed-Efficiency Product vs. Effective Voltage for an NMOS device. The                                                                                                      | ,) |

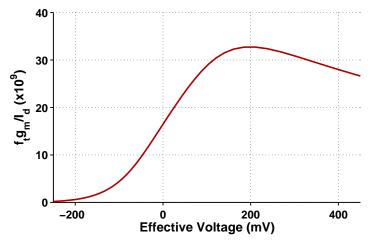

| 5.0        | optimal effective voltage is 155 mV.                                                                                                                                        | 81 |

|            |                                                                                                                                                                             | 01 |

| 5.9  | Speed-Efficiency Product vs. Effective Voltage for a PMOS device. The opti-<br>mal effective voltage is 205 mV. | 81  |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

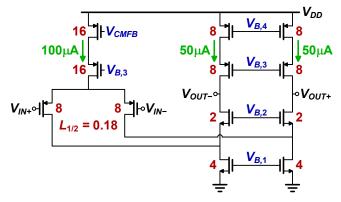

| 5.10 | Transistors sizes for the folded-cascode OTA. All sizes are in microns, and all                                 |     |

|      | transistor lengths are 0.24 µm unless otherwise noted                                                           | 82  |

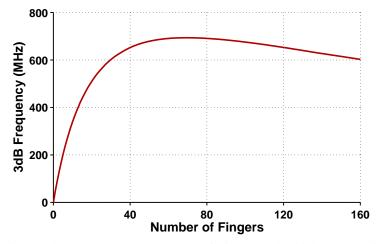

| 5.11 | 3 dB-Frequency vs. Number of Fingers. The highest bandwidth occurs with 69                                      |     |

|      | fingers.                                                                                                        | 83  |

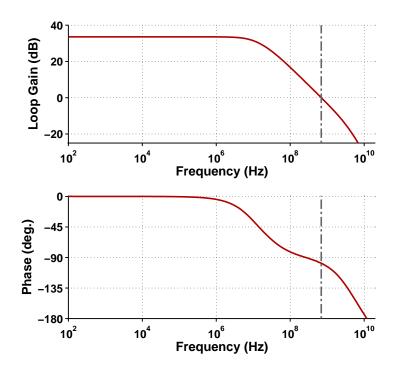

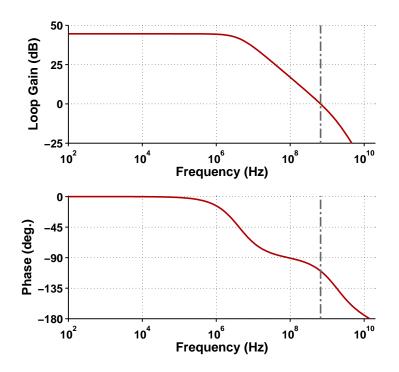

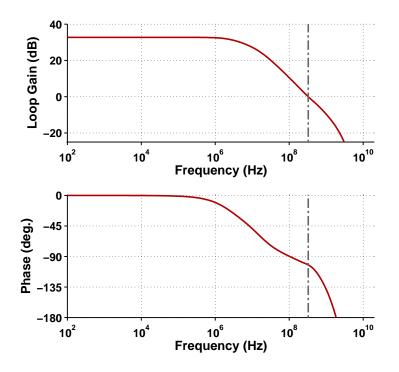

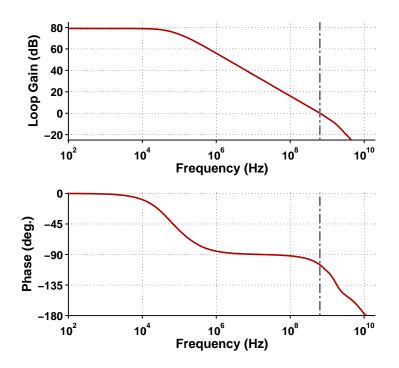

| 5.12 | Bode plot of the folded-cascode OTA with 64 fingers.                                                            | 84  |

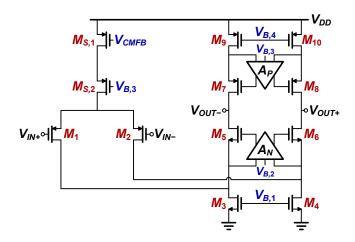

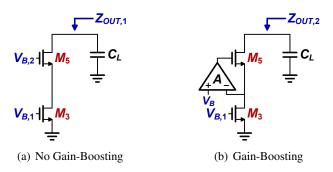

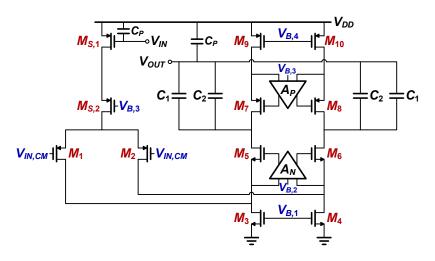

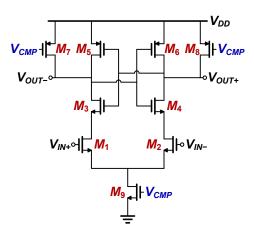

|      | Gain-boosted folded-cascode OTA.                                                                                | 85  |

|      | Output impedance without and with gain-boosting.                                                                | 86  |

| 5.15 | Folded-cascode OTA with NMOS input for gain-boosting amplifier $A_P$                                            | 88  |

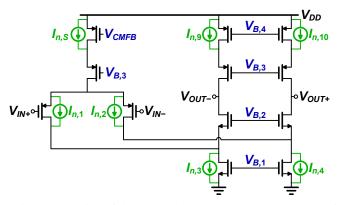

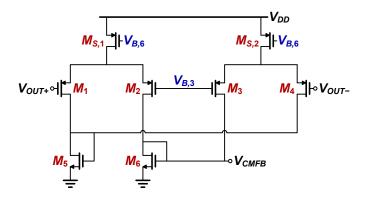

| 5.16 | CMFB circuit for gain-booster $A_P$ (Fig. 5.15)                                                                 | 89  |

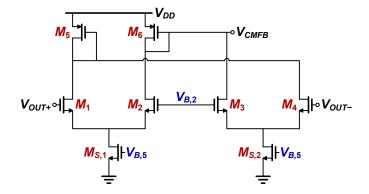

| 5.17 | CMFB circuit for gain-booster $A_N$ (Fig. 5.6)                                                                  | 90  |

| 5.18 | Bode plot of gain-booster $A_P$ (Fig. 5.15)                                                                     | 91  |

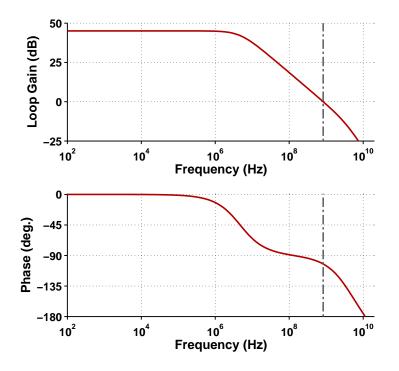

| 5.19 | Bode plot of gain-booster $A_N$ (Fig. 5.6).                                                                     | 92  |

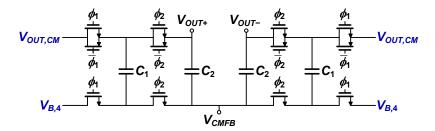

|      | Switched-capacitor common-mode feedback.                                                                        | 93  |

| 5.21 | Stability analysis of the CMFB loop                                                                             | 93  |

|      | Bode plot of the switched-capacitor CMFB loop.                                                                  | 95  |

| 5.23 | Bode plot of the gain-boosted folded-cascode OTA.                                                               | 96  |

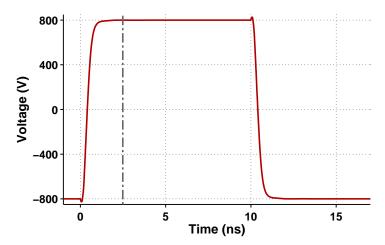

| 5.24 | Settling behaviour of the gain-boosted folded-cascode OTA with a full-scale                                     |     |

|      | output votlage between $\pm 800 \text{mV}$ .                                                                    | 96  |

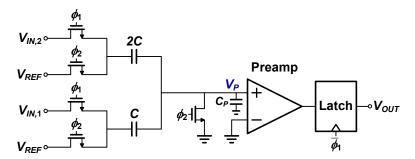

| 5.25 | Comparator with passive summer. The feed-forward input from the previous                                        |     |

|      | stage $V_{IN,2}$ is added to the OTA output from the current stage $V_{IN,1}$                                   | 98  |

|      | Preamplifier for the summing comparator                                                                         | 99  |

| 5.27 | Latch for the summing comparator                                                                                | 99  |

| 5.28 | Simulation for finding latch mode time constant                                                                 | 100 |

| 5.29 | D/A converter voltages control two separate branches at the input of the integrator.                            | 101 |

| 5.30 | Eight separate switches of the integrator stages. While there are more switches                                 |     |

|      | from the two-phase resetting scheme and the separate input branch from the                                      |     |

|      | D/A converter, they only replicate the eight switches shown here                                                |     |

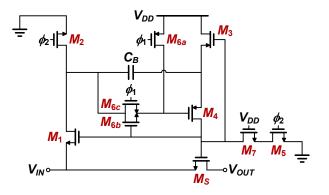

| 5.31 | Bootstrapping circuit for sampling transistor $M_S$                                                             | 103 |

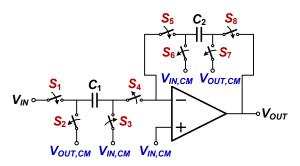

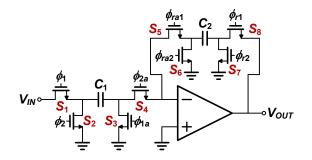

| 5.32 | Bottom-plate sampling using an advanced clock on switches $S_3$ to $S_6$                                        | 104 |

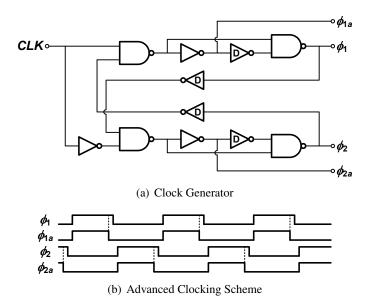

| 5.33 | Non-overlapping clock generator with advanced clocking scheme                                                   | 105 |

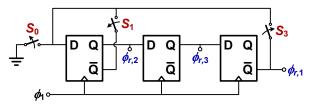

| 5.34 | Clock divider for an incremental A/D converter with operation at an OSR of 1,                                   |     |

|      | 3 or infinity                                                                                                   | 105 |

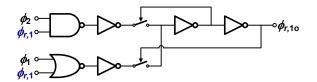

|      | Non-overlapping reset clock generator.                                                                          | 106 |

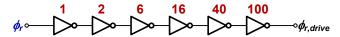

| 5.36 | Clock driver with sizes relative to a unit-sized inverter $(1 \mu m/0.18 \mu m NMOS)$                           |     |

|      | and 3 $\mu m/0.18\mu m$ PMOS)                                                                                   | 106 |

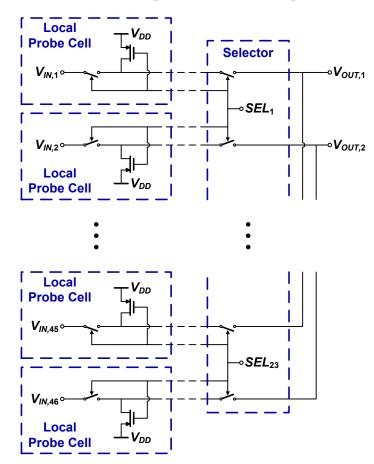

| 5.37 | Analog multiplexer with two local probe cells for each selector portion of the                                  |     |

|      | circuit. Each output node is tied to 23 parallel multiplexer cells, resulting in 23                             |     |

|      | selector signals from 23 shift registers                                                                        | 107 |

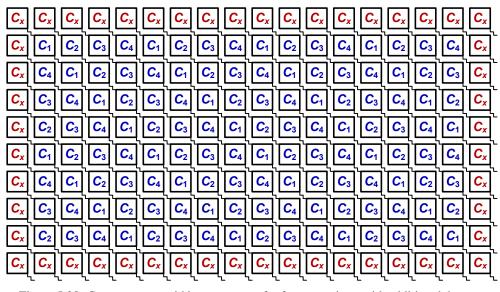

| 5.38 | Common-centroid layout pattern for four capacitors with additional dummy                                        |     |

|      | capacitors $C_x$                                                                                                | 108 |

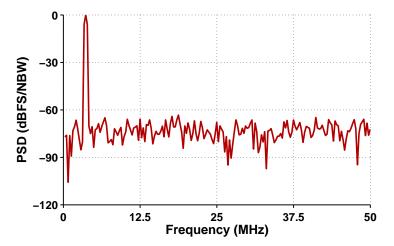

| 5.39  | Simulated output spectrum for the $8^{\text{th}}$ -order incremental A/D converter (NBW = 391 kHz). The SNDR is 75.9 dB. | 110  |

|-------|--------------------------------------------------------------------------------------------------------------------------|------|

| 5 40  | Simulated output spectrum for the 8-stage pipeline A/D converter (NBW $=$                                                | 110  |

| 2.10  | 391  kHz). The SNDR is $50.3  dB$ .                                                                                      | 110  |

| 5.41  | Simulated output spectrum for the 8 <sup>th</sup> -order cascaded $\Delta\Sigma$ modulator (NBW =                        | 110  |

| 0111  | 391  kHz). The SNDR is $67.4  dB$ .                                                                                      | 111  |

|       | ,                                                                                                                        |      |

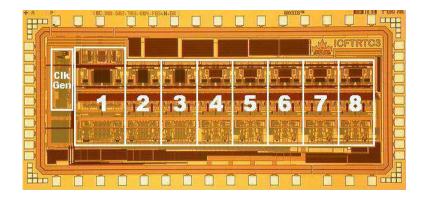

| 6.1   | Chip micrograph. The active area is 2.7 mm by 1.0 mm                                                                     |      |

| 6.2   | 4-layer PCB photo (178 mm by 127 mm)                                                                                     | 113  |

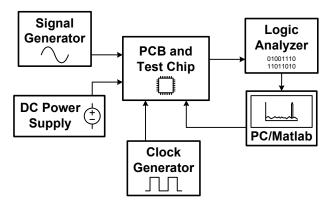

| 6.3   | Equipment test setup surrounding the PCB and test chip. The PC controls the                                              |      |

|       | various settings of the test chip                                                                                        | 114  |

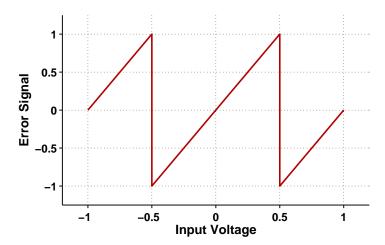

| 6.4   | Pipeline stage error signal using the same reference voltages as those in the                                            |      |

|       | incremental mode                                                                                                         | 116  |

| 6.5   | Two output codes that give the same histogram when using a histogram based                                               |      |

|       | INL/DNL measurement.                                                                                                     | 118  |

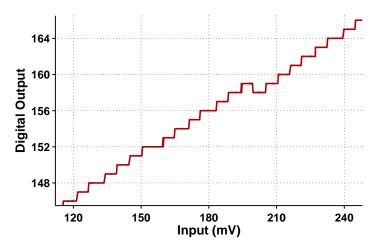

| 6.6   | Portion of the output versus input curve for the pipeline A/D converter with a                                           |      |

|       | gain error.                                                                                                              | 119  |

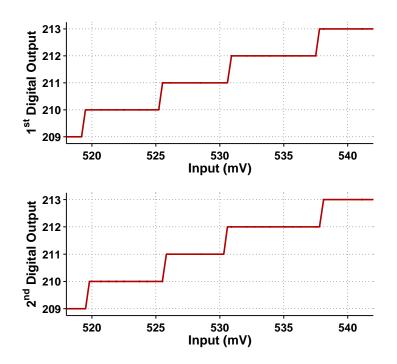

| 6.7   | Differing transition points of the two outputs on alternating phases of the pipeline                                     |      |

|       | A/D converter                                                                                                            |      |

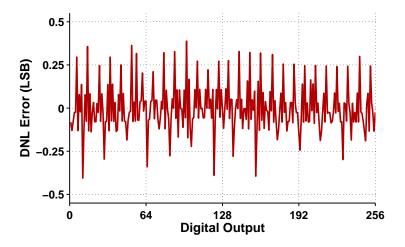

| 6.8   | Differential non-linearity error.                                                                                        |      |

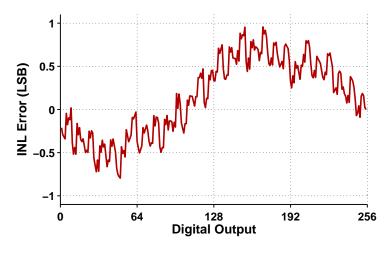

| 6.9   | Integral non-linearity error.                                                                                            | 121  |

| 6.10  | Output spectrum for the 8-stage pipeline A/D converter with an input at 1.9 MHz                                          |      |

|       | (NBW = 4.6  kHz).                                                                                                        |      |

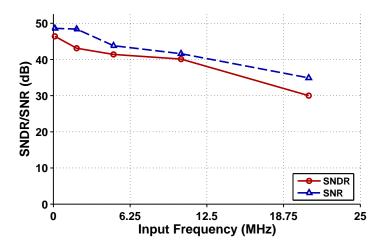

|       | SNDR and SNR versus input frequency in the pipeline mode.                                                                | 122  |

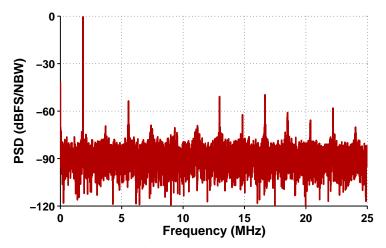

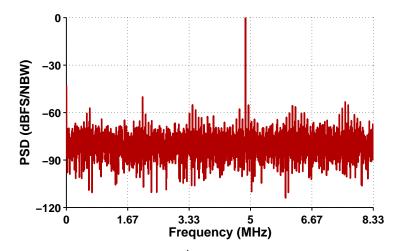

| 6.12  | Output spectrum for the 8 <sup>th</sup> -order cascaded $\Delta\Sigma$ with an input at 2.1 MHz (NBW =                   | 100  |

| ( 10  | 2.3kHz)                                                                                                                  | 123  |

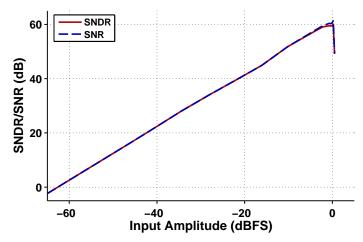

| 6.13  | SNDR and SNR vs. Input Amplitude at an input frequency of 2.1 MHz. SNDR                                                  | 10.4 |

| C 1 4 | and SNR are similar and deviate by 1.2 dB at the peak.                                                                   | 124  |

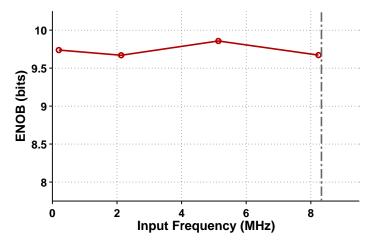

| 6.14  | ENOB vs. Input Frequency. For the inputs at 5.2 MHz and 8.3 MHz, a two-                                                  |      |

|       | tone measurement was made to ensure the harmonics were present in-band and                                               | 105  |

| 6 15  | added in the ENOB calculation                                                                                            | 123  |

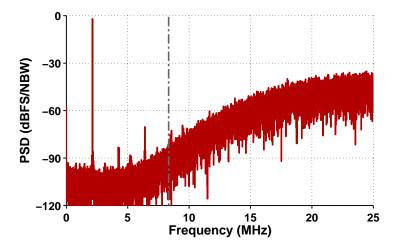

| 0.15  | input at 4.9 MHz (NBW = $3.1 \text{ kHz}$ ).                                                                             | 176  |

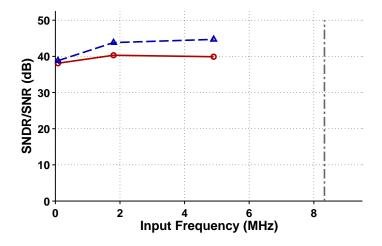

| 6 1 6 | SNDR and SNR versus input frequency in the incremental mode                                                              |      |

|       | Non-overlapping resetting clocks in the presence of parasitic resistances and                                            | 121  |

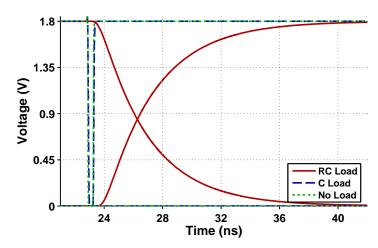

| 0.17  | capacitances.                                                                                                            | 120  |

|       |                                                                                                                          | 129  |

| A.1   | A $2^{nd}$ -order input feed-forward cascaded incremental A/D converter                                                  | 138  |

| C.1   | Algorithmic data converter.                                                                                              | 147  |

| C.2   | Time-interleaved 1 <sup>st</sup> -order incremental data converter derived from an unwound                               |      |

|       | incremental data converter.                                                                                              | 150  |

| C.3 | Time-interleaved 2 <sup>nd</sup> -order incremental data converter derived from an un- |

|-----|----------------------------------------------------------------------------------------|

|     | wound incremental data converter                                                       |

| C.4 | Time-interleaved 1-1 cascaded 2 <sup>nd</sup> -order incremental data converter        |

# List of Abbreviations

| ADSL | Asymmetric Digital Subscriber Line      |

|------|-----------------------------------------|

| A/D  | Analog-to-Digital                       |

| CMFB | Common-Mode Feedback                    |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| CMRR |                                         |

| CQFP | Ceramic Quad Flat Pack                  |

| DNL  | Differential Non-Linearity              |

| D/A  | Digital-to-Analog                       |

| ENOB | Effective Number of Bits                |

| FFT  | Fast Fourier Transform                  |

| FR-4 | Flame Retardant 4                       |

| INL  | Integral Non-Linearity                  |

| LSB  | Least Significant Bit                   |

| MASH | Multi-Stage Noise-Shaping               |

| MSB  | Most Significant Bit                    |

|      | N-channel Metal-Oxide-Semiconductor     |

| NTF  | Noise Transfer Function                 |

| OSR  | Oversampling Ratio                      |

| ОТА  | Operational Transconductance Amplifier  |

| PCB  | Printed Circuit Board                   |

| PMOS | P-channel Metal-Oxide-Semiconductor     |

| PSD  | Power Spectral Density                  |

| SFDR | Spurious-Free Dynamic Range             |

| SNDR | Signal-to-Noise and Distortion Ratio    |

| SNR  | Signal-to-Noise Ratio                   |

| SQNR | Signal-to-Quantization Noise Ratio      |

| STF  | Signal Transfer Function                |

| S/H  | Sample-and-Hold                         |

## **Chapter 1**

## Introduction

**D** ELTA-SIGMA ( $\Delta\Sigma$ ) modulation efficiently performs high resolution data conversion using oversampling. With increasing bandwidth demands, reducing the *oversampling ratio* (OSR) is important to meet the required input bandwidth while also attaining medium to high resolution as expected from oversampled converters. The purpose of this research is to investigate the effect of reducing the OSR of  $\Delta\Sigma$  modulators and incremental data converters.

## **1.1** Motivation

High-speed data converters operating on input signal bandwidths in the megahertz range are key analog building blocks for a variety of applications including high-speed wireless and wireline communication systems, high-quality video systems, imaging systems, and instrumentation systems. A few examples include lower-bandwidth applications such as *asymmetric digital subscriber line* (ADSL) which require 14 bit resolution with a 2.2 MHz signal bandwidth [1], higher speed television receivers which require a bandwidth of 8 MHz per channel but only 9 bit resolution [2], or high-speed video decoding which requires data conversion at sampling frequencies as high as 150 MHz at 10 bit resolution [3].

When higher accuracy but lower bandwidth is needed, oversampling techniques are typically employed. High OSRs are desirable since the requirements on the individual circuits are relaxed based on the OSR. However, increased bandwidth requirements necessitate techniques to reduce the OSR while still attaining good performance. The most common oversampled data converter is the  $\Delta\Sigma$  modulator which efficiently performs high-resolution data conversion and is typically reserved for high OSR applications where noise-shaping increases the *signal-to-quantization noise ratio* (SQNR). The difficulty at low OSRs is that noise-shaping is not as efficient because it increases the total noise power in the system thereby reducing the SQNR. Oversampled cascaded or *multi-stage noise-shaping* (MASH) architectures provide an alternative as they are more stable than single-stage architectures [4], but are more sensitive to non-idealities in the circuit.

Nyquist-rate *analog-to-digital* (A/D) converters can be used at low OSRs [5], and they typically require some oversampling to reduce the requirements on the anti-aliasing filter at the input. However, they lose a significant advantage provided by noise-shaping since input-referred noise gets shaped by gain stages rather than the integrators present in noise-shaping converters. This is a fundamental disadvantage of pipeline A/D converters when compared to  $\Delta\Sigma$  modulators.

## **1.2 Current Literature**

#### **1.2.1** High-Speed $\Delta\Sigma$ Modulators

In the last several years there has been considerable research on high-speed  $\Delta\Sigma$  modulators with OSRs of 16 or less. Table 1.1 summarizes some experimental results in *complementary metal-oxide-semiconductor* (CMOS) technology for recently published high-speed  $\Delta\Sigma$  modulators with OSRs of 16 or less.

The modulators with the highest sampling frequencies are continuous-time. This is expected since the maximum sampling frequency of continuous-time modulators is dependent on the feedback path which includes the quantizer regeneration time and the feedback *digital-to-analog* (D/A) converter, while discrete-time modulators depend on the *opera-tional transconductance amplifier* (OTA) settling [4]. Despite their inferior speed, discrete-time modulators are still shown to operate at sampling frequencies of 100 MHz or more.

The lowest reported OSR for a cascaded architecture is 4 [11, 14]. To the author's knowledge, no implementation of a cascaded  $\Delta\Sigma$  modulator exists with a lower OSR. In this dissertation a 10-bit 8-stage cascaded  $\Delta\Sigma$  architecture with an OSR of 3 is proposed, as well as an 11-bit 8-stage cascaded incremental A/D converter. Both the low OSR and high number of cascaded stages have never been implemented before.

| Ref. | Technology | Architecture                  | Sampling<br>Frequency | Signal<br>Bandwidth | OSR  | SNDR            | Power  |

|------|------------|-------------------------------|-----------------------|---------------------|------|-----------------|--------|

| [6]  | 0.25 µm    | 5 <sup>th</sup> -order (C)    | 60 MHz                | 2.5 MHz             | 12   | 80 dB           | 50 mW  |

| [7]  | 0.18 µm    | 0-3 MASH (D)                  | 50 MHz                | 3.1 MHz             | 8    | 64 dB           | 22 mW  |

| [8]  | 90 nm      | 4 <sup>th</sup> -order (D)    | 100 MHz               | 4 MHz               | 12.5 | 67 dB           | 12 mW  |

| [9]  | 0.18 µm    | 2 <sup>nd</sup> -order TI (D) | 100 MHz               | 4.2 MHz             | 12   | 79 dB           | 28 mW  |

| [10] | 0.18 µm    | 2-1 MASH (C/D)                | 240 MHz               | 7.5 MHz             | 16   | 67 dB           | 89 mW  |

| [11] | 0.13 µm    | 1-2 MASH (D)                  | 80 MHz                | 10 MHz              | 4    | $50\mathrm{dB}$ | 60 mW  |

| [12] | 0.18 µm    | 3 <sup>rd</sup> -order TI (C) | 100 MHz               | 10 MHz              | 5    | 57 dB           | 101 mW |

| [13] | 0.18 µm    | 2-2 MASH (C)                  | 160 MHz               | 10 MHz              | 8    | 57 dB           | 122 mW |

| [14] | 0.18 µm    | 2-0 MASH (D)                  | 80 MHz                | 10 MHz              | 4    | 73 dB           | 240 mW |

| [15] | 0.25 µm    | 2 <sup>nd</sup> -order (C)    | 320 MHz               | 10 MHz              | 16   | 54 dB           | 15 mW  |

| [16] | 0.18 µm    | 4 <sup>th</sup> -order (C)    | 276 MHz               | 11.5 MHz            | 12   | 69 dB           | 21 mW  |

| [17] | 0.18 µm    | 5 <sup>th</sup> -order (D)    | 200 MHz               | 12.5 MHz            | 8    | 72 dB           | 200 mW |

| [18] | 0.13 µm    | 4 <sup>th</sup> -order (C)    | 300 MHz               | 15 MHz              | 10   | 64 dB           | 70 mW  |

| [12] | 0.18 µm    | 3 <sup>rd</sup> -order TI (C) | 200 MHz               | 20 MHz              | 5    | 49 dB           | 103 mW |

| [11] | 0.13 µm    | 1-2 MASH (D)                  | 160 MHz               | 20 MHz              | 4    | $50\mathrm{dB}$ | 87 mW  |

| [19] | 0.13 µm    | 3 <sup>rd</sup> -order (C)    | 640 MHz               | 20 MHz              | 16   | 74 dB           | 58 mW  |

Table 1.1: Recently published experimental results for high-speed continuous-time (C) and discrete-time (D)  $\Delta\Sigma$  modulators at low OSRs in CMOS technology, in order of increasing signal bandwidth.

### **1.2.2 High-Speed Pipeline A/D Converters**

Current research in high-speed pipeline A/D converters shows that in CMOS technology only a few implementations exist with sampling frequencies greater than 200 MHz, and those data converters have resolutions less than 9 bits, where resolution refers to *signal-to-noise and distortion ratio* (SNDR). Table 1.2 summarizes these recent experimental results.

The results of Table 1.2 are a good indicator of the maximum sampling frequency for discrete-time  $\Delta\Sigma$  modulators. Pipeline A/D converters have slightly higher maximum sampling frequencies than discrete-time  $\Delta\Sigma$  modulators, but it will be shown that the design of cascaded  $\Delta\Sigma$  modulators at low OSRs is similar to the design of pipeline A/D converters,

| Ref. | Technology | Sampling<br>Frequency | Signal<br>Bandwidth | SNDR  | Power           |

|------|------------|-----------------------|---------------------|-------|-----------------|

| [20] | 0.18 µm    | 100 MHz               | 50 MHz              | 54 dB | 67 mW           |

| [21] | 0.18 µm    | 100 MHz               | 50 MHz              | 55 dB | 33 mW           |

| [22] | 0.18 µm    | 100 MHz               | 50 MHz              | 72 dB | 230 mW          |

| [23] | 90 nm      | 100 MHz               | 50 MHz              | 73 dB | 250 mW          |

| [24] | 90 nm      | $100\mathrm{MHz}$     | 50 MHz              | 70 dB | 130 mW          |

| [25] | 0.18 µm    | $110\mathrm{MHz}$     | 55 MHz              | 64 dB | 97 mW           |

| [26] | 0.18 µm    | 125 MHz               | 62.5 MHz            | 53 dB | $40\mathrm{mW}$ |

| [27] | 0.18 µm    | 125 MHz               | 62.5 MHz            | 69 dB | 909 mW          |

| [28] | 0.18 µm    | 125 MHz               | 62.5 MHz            | 78 dB | 385 mW          |

| [29] | 0.18 µm    | 150 MHz               | 75 MHz              | 52 dB | 123 mW          |

| [30] | 0.25 µm    | 180 MHz               | 90 MHz              | 63 dB | 756 mW          |

| [31] | 0.18 µm    | 200 MHz               | 100 MHz             | 48 dB | 30 mW           |

| [32] | 0.13 µm    | 200 MHz               | 100 MHz             | 52 dB | 104 mW          |

| [33] | 90 nm      | 200 MHz               | 100 MHz             | 54 dB | $55\mathrm{mW}$ |

| [34] | 90 nm      | 200 MHz               | 100 MHz             | 62 dB | 348 mW          |

| [27] | 90 nm      | 205 MHz               | 102.5 MHz           | 54 dB | 61 mW           |

| [35] | 0.13 µm    | 220 MHz               | 110 MHz             | 54 dB | 135 mW          |

| [36] | 0.13 µm    | 250 MHz(x4)           | 125 MHz(x4)         | 55 dB | 250 mW          |

| [37] | 0.13 µm    | 400 MHz               | 200 MHz             | 54 dB | 160 mW          |

| [38] | 90 nm      | 500 MHz               | 250 MHz             | 53 dB | 55 mW           |

Table 1.2: Recently published experimental results for high-speed pipeline A/D converters in CMOS technology.

and for that reason  $\Delta\Sigma$  modulators should attain equally fast sampling frequencies.

## 1.3 Outline

The dissertation is organized as follows: Chapter 2 provides some background information on the various A/D converter architectures necessary for understanding the material pre-

sented. Chapter 3 discusses the operation of  $\Delta\Sigma$  modulators at low OSRs while Chapter 4 presents the operation of incremental A/D converters at low OSRs. The design of a prototype chip fabricated in 0.18 µm CMOS technology is described in Chapter 5, and Chapter 6 presents the experimental results from the prototype in its three modes of operation as a pipeline A/D converter, a  $\Delta\Sigma$  modulator and an incremental A/D converter. Chapter 7 concludes the dissertation. Derivations of the incremental A/D converter resolution and the DC gain requirements of the incremental A/D converter are given in Appendix A and Appendix B, respectively. An alternative implementation to the time-interleaved incremental data converter architecture presented in Chapter 4 is given in Appendix C.

# **Chapter 2**

## Background Information

The basic operation of various data converters, including  $\Delta\Sigma$  modulators, incremental A/D converters, pipeline A/D converters and time-interleaved A/D converters are explained in this chapter. The fundamental trade-offs between power, resolution and bandwidth are also discussed.

## **2.1** $\Delta\Sigma$ Modulators

$\Delta\Sigma$  modulators employ both oversampling and noise-shaping to improve the accuracy of a low-resolution (as low as 1-bit) internal A/D converter, or quantizer. With the feedback loop the noise in the quantizer has a different transfer function to the output than the signal. This allows the designer to choose a filter that will shape the noise and keep it small in the band of interest (which is dependent on the OSR), while also keeping the signal unattenuated in this frequency range.

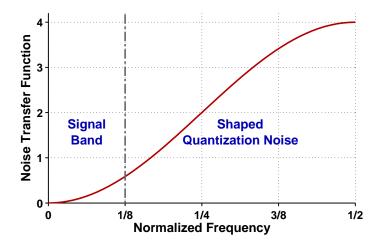

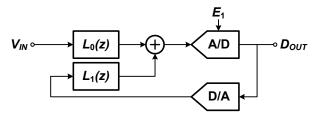

As shown in Fig. 2.1, only a small portion of the frequency band is kept through digital filtering leaving little noise within the band of interest, resulting in a high-resolution A/D converter at a reduced speed. The *noise transfer function* (NTF) and the *signal transfer function* (STF) characterize the  $\Delta\Sigma$  modulator. Referring to Fig. 2.2 (assuming an internal A/D and D/A reference voltage  $V_{REF}$  with  $D_1 \in [-1, 1]$ ), the NTF is

$$\frac{D_{OUT} \cdot V_{REF}}{E_1} = \frac{1}{1 - L_1(z)}$$

(2.1)

Figure 2.1: Spectral operation of a  $\Delta\Sigma$  modulator.

while the STF is

$$\frac{D_{OUT} \cdot V_{REF}}{V_{IN}} = \frac{L_0(z)}{1 - L_1(z)}.$$

(2.2)

The order and shape of the transfer functions, the OSR, and the internal A/D converter resolution determine the resolution of the  $\Delta\Sigma$  modulator.

Figure 2.2: General architecture of a  $\Delta\Sigma$  modulator characterized by the two loop filters  $L_0(z)$  and  $L_1(z)$  (without the decimation filter).

### **2.1.1** Single-Stage $\Delta \Sigma$ Modulators

A generalized single-stage modulator was shown in Fig. 2.2. They are characterized by a single quantizer, NTF and STF. High resolution  $\Delta\Sigma$  modulators are designed with high OSRs, high-order NTFs, and multi-bit quantizers [4]. For high-bandwidth applications the OSR must be reduced, leaving only the NTF and quantizer resolution as a design parameter for increased resolution.

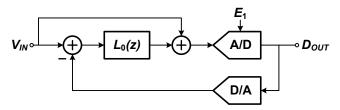

One significant improvement in  $\Delta\Sigma$  modulators is the use of an input feed-forward path [39]. An extra feed-forward branch is added from the input to the summer in front of the quantizer. With this architecture, the NTF remains unchanged, but the STF is

$$\frac{D_{OUT} \cdot V_{REF}}{V_{IN}} = \frac{1 + L_0(z)}{1 - L_1(z)}.$$

(2.3)

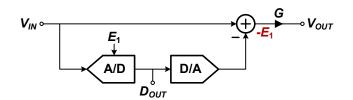

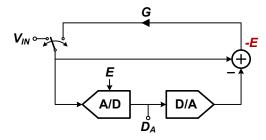

For the input feed-forward architecture, if  $L_0(z) = -L_1(z)$  the STF becomes unity. This modifies the general structure of Fig. 2.2 to that shown in Fig. 2.3. More important than the unity-gain STF, the signal content at the loop filter output is minimized. Shown in Fig. 2.3, the delay-free path from the input through the A/D and D/A comes back and subtracts from the input. No signal content enters the loop filter, and all that is left is the error signal  $E_1$ . Therefore, the loop filter output is only a function of  $E_1$ .  $E_1$  will always be somewhat correlated with the input, but for a higher-resolution internal A/D converter the input will be less correlated, and distortion introduced by the loop filter will be less signal dependent. This is advantageous as low-distortion OTAs become more difficult to design with increasingly smaller power supplies [40, 41].

Figure 2.3: Input feed-forward architecture for a general  $\Delta\Sigma$  modulator (without the decimation filter).

### **2.1.2** Cascaded $\Delta\Sigma$ Modulators

For stability reasons, it is difficult to design a high-order NTF and keep it stable as the filter coefficients vary, or the loop becomes nonlinear. There is also a trade-off between the NTF stability and how aggressively it shapes the noise (i.e., how much resolution it obtains). For these reasons high-resolution or low OSR  $\Delta\Sigma$  modulators are often implemented with cascaded architectures.

As the name implies, cascaded (or MASH)  $\Delta\Sigma$  modulators cascade two or more singlestage  $\Delta\Sigma$  modulators. They are named based on the order of each stage; a 2-1 MASH  $\Delta\Sigma$  cascades a 2<sup>nd</sup>-order  $\Delta\Sigma$  with a 1<sup>st</sup>-order  $\Delta\Sigma$ . An L - 0 Leslie-Singh architecture [42], or 0 - L architecture [43] refers to an  $L^{\text{th}}$ -order  $\Delta\Sigma$  followed or proceeded by a Nyquist-rate A/D converter, where the Nyquist-rate converter is loosely considered a 0<sup>th</sup>-order  $\Delta\Sigma$ .

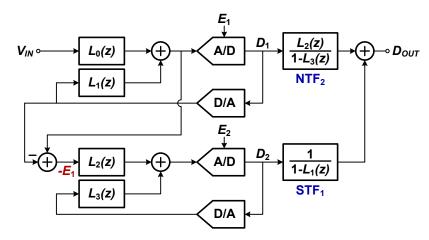

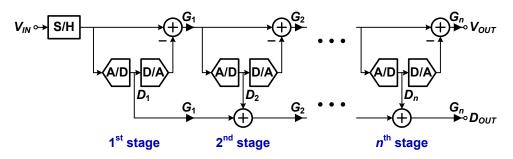

A general two-stage cascaded  $\Delta\Sigma$  modulator is shown in Fig. 2.4. The advantage of cascaded modulators is that no individual modulator needs to be designed with a high-order filter; the total filter order can be spread out across many different stages so that each individual  $\Delta\Sigma$  stage will only be of lower order (1<sup>st</sup>-order, 2<sup>nd</sup>-order, or maybe 3<sup>rd</sup>-order). The modulator stability will be a function of the individual lower order modulators rather than the total order of the modulator.

Figure 2.4: General 2-stage cascaded  $\Delta\Sigma$  modulator where loop filters  $L_0(z)$  and  $L_1(z)$  characterize the first stage, and  $L_2(z)$  and  $L_3(z)$  characterize the second stage.

A digital filter is required to recombine the digital outputs of the individual  $\Delta\Sigma$  modulators. It is designed to cancel the error introduced in the first stages, leaving only the error introduced in the last of the cascaded stages which will be noise-shaped by the product of the NTF of each stage. This cancelation is dependent on matching between the digital filters and the analog filters within the individual  $\Delta\Sigma$  modulators; this is one of the major limitations for high-resolution cascaded  $\Delta\Sigma$  modulators [44].

As shown in Fig. 2.4, when the error signal  $-E_1$  is passed to the next stage, the output of each of the individual modulators are

$$D_1 \cdot V_{REF} = V_{IN} \frac{L_0(z)}{1 - L_1(z)} + E_1 \frac{1}{1 - L_1(z)}$$

(2.4)

and

$$D_2 \cdot V_{REF} = -E_1 \frac{L_2(z)}{1 - L_3(z)} + E_2 \frac{1}{1 - L_3(z)}.$$

(2.5)

In order to cancel the error signal  $E_1$ ,  $D_1 \cdot V_{REF}$  is multiplied by the second stage NTF, and  $D_2$  is multiplied by the first stage STF. The resulting output is

$$D_{OUT} \cdot V_{REF} = D_1 \cdot V_{REF} \frac{L_2(z)}{1 - L_3(z)} + D_2 \cdot V_{REF} \frac{1}{1 - L_1(z)}$$

$$= V_{IN} \frac{L_0(z)}{1 - L_1(z)} \frac{L_2(z)}{1 - L_3(z)} + E_2 \frac{1}{1 - L_1(z)} \frac{1}{1 - L_3(z)}$$

$$= V_{IN} \cdot \text{STF}_1 \cdot \text{STF}_2 + E_2 \cdot \text{NTF}_1 \cdot \text{NTF}_2.$$

(2.6)

It is clear that  $D_{OUT}$  is no longer a function of  $E_1$ , and the overall NTF on the error signal  $E_2$  is the cascaded NTF of both individual stages (NTF<sub>1</sub> and NTF<sub>2</sub>), while the overall STF on the input signal  $V_{IN}$  is the cascaded STF of both individual stages (STF<sub>1</sub> and STF<sub>2</sub>).

As mentioned above, when the input feed-forward architecture is used, the loop filter output contains no signal component. Depending on the quantizer resolution, this error signal might be considerably smaller than the input range of a  $\Delta\Sigma$  modulator. When the error signal is passed to the subsequent stage, it may be possible to amplify it while staying within the allowable input range. The amplification factor will increase the overall resolution of the cascaded  $\Delta\Sigma$  by the same amount.

With the input feed-forward architecture, the loop filter can be manipulated so that the integrator output is a delayed version of the error signal. An example of this in a 2-1 cascaded  $\Delta\Sigma$  modulator is shown in Fig. 2.5. The first stage has an NTF of  $(1-z^{-1})^2$  while the second stage has an NTF of  $(1-z^{-1})$ . The second integrator output in the first stage is the inverted error signal from the first quantizer  $-E_1$ , delayed by two samples. Assuming it is small enough (equivalently, the quantizer resolution is high enough), it can be multiplied by an interstage gain factor G. After the digital cancellation filter, the final output is

$$D_{OUT} \cdot V_{REF} = z^{-3} V_{IN} + \frac{(1 - z^{-1})^3}{G} E_2.$$

(2.7)

The overall NTF is  $(1 - z^{-1})^3/G$ , the expected 3<sup>rd</sup>-order NTF  $(1 - z^{-1})^3$  reduced by the interstage gain factor *G*. The STF is simply the input  $V_{IN}$  delayed by three samples. Since the second stage output is a delayed version of its error signal  $E_2$ , this could easily be passed

Figure 2.5: Input feed-forward 2-1 cascaded  $\Delta\Sigma$  modulator. The interstage gain G improves the resolution by G.

on to a third stage with additional cascading.

## 2.2 Incremental Data Converters

Incremental A/D converters are best understood as a combination of  $\Delta\Sigma$  modulators and dual-slope A/D converters. They act like dual-slope A/D converters mixed in time, but also have the benefit of utilizing higher-order loop filters like  $\Delta\Sigma$  modulators.

### 2.2.1 Dual-Slope A/D Converters

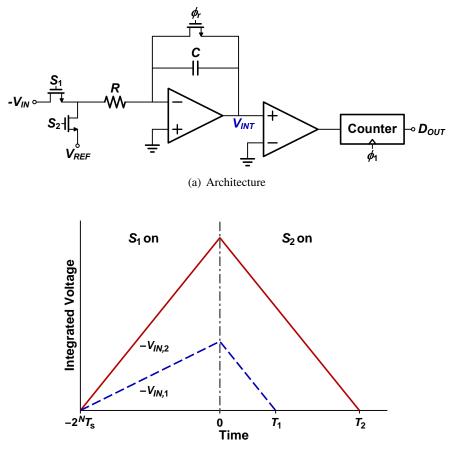

The dual-slope (or integrating) A/D converter is useful for high-accuracy, high-linearity conversion with low offset and gain errors [45]. Shown in Fig. 2.6, the converter integrates the input signal for a fixed time and then subtracts a reference voltage for a counted number of clock periods until the output crosses zero. The final count at the zero crossing is the resulting digital output. For an *N*-bit A/D converter,  $2^{N+1}$  cycles are required for one conversion. For high-resolution A/D converters the conversion time can severely limit the speed at which they operate.

During the first phase when  $S_1$  is on, the input  $-V_{IN}$  is integrated. After  $2^N$  clock cycles

(b) Time-Domain Integrator Output

Figure 2.6: Dual-slope A/D converter. The input signal is integrated on  $S_1$  while the reference voltage is integrated and subtracted from the input on  $S_2$ .  $\phi_1$  is operating at the sampling frequency  $f_s$ .  $T_1$  and  $T_2$  are proportional to their respective digital outputs.

(the entire  $S_1$  phase), the integrator output will be

$$V_{INT} = -\int_{-2^{N}T_{s}}^{0} \frac{-V_{IN}}{RC} d\tau = \frac{V_{IN}}{RC} \cdot 2^{N}T_{s}.$$

(2.8)

On the second phase,  $S_1$  is off and  $S_2$  is on.  $V_{REF}$  is then integrated until the voltage at  $V_{INT}$  goes to zero. The voltage at the integrator output during  $S_2$  is

$$V_{INT} = -\int_0^t \frac{V_{REF}}{RC} dt + \frac{V_{IN}}{RC} \cdot 2^N T_s.$$

(2.9)

After t seconds, the voltage is

$$V_{INT} = \frac{V_{IN} \cdot 2^N T_s - V_{REF} \cdot t}{RC}.$$

(2.10)

This voltage is zero when

$$t_0 = \frac{V_{IN}}{V_{REF}} \cdot 2^N T_s. \tag{2.11}$$

It is clear from this equation that the time  $t_O$  when  $V_{INT}$  crosses zero is proportional to the ratio of  $V_{IN}/V_{REF}$  discretized in steps of  $T_s$ , where  $T_s$  is the time-domain *least significant bit* (LSB) of the *N*-bit output.

If  $V_{IN}$  has a frequency dependent component  $(V_{IN,\sim})$  along with a constant input  $(V_{IN,-})$ , then the output of the first integration phase is

$$V_{INT} = \int_{-2^{N}T_{s}}^{0} \frac{V_{IN}}{RC} d\tau$$

=  $\int_{-2^{N}T_{s}}^{0} \frac{V_{IN,-} + V_{IN,\sim}}{RC} d\tau$

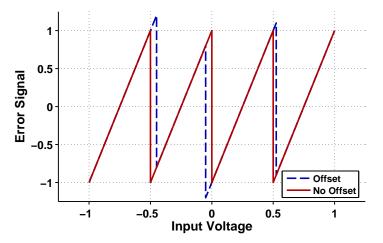

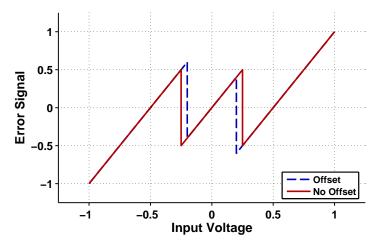

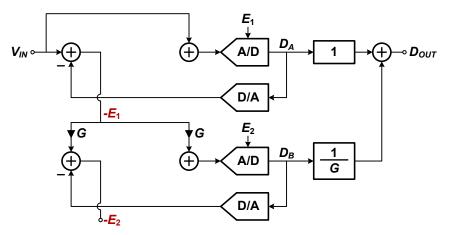

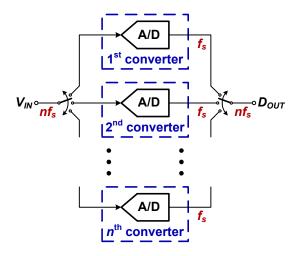

=  $\frac{V_{IN,-}}{RC} \cdot 2^{N}T_{s} + \int_{-2^{N}T_{s}}^{0} \frac{V_{IN,\sim}}{RC} d\tau.$  (2.12)